#### Errata

Title & Document Type: 3586A/B/C Service Manual

Manual Part Number: 03586-90000

#### **HP References in this Manual**

This manual may contain references to HP or Hewlett-Packard. Please note that Hewlett-Packard's former test and measurement, semiconductor products and chemical analysis businesses are now part of Agilent Technologies. We have made no changes to this manual copy. The HP XXXX referred to in this document is now the Agilent XXXX. For example, model number HP8648A is now model number Agilent 8648A.

#### **About this Manual**

We've added this manual to the Agilent website in an effort to help you support your product. This manual provides the best information we could find. It may be incomplete or contain dated information, and the scan quality may not be ideal. If we find a better copy in the future, we will add it to the Agilent website.

#### **Support for Your Product**

Agilent no longer sells or supports this product. You will find any other available product information on the Agilent Test & Measurement website:

#### www.tm.agilent.com

Search for the model number of this product, and the resulting product page will guide you to any available information. Our service centers may be able to perform calibration if no repair parts are needed, but no other support from Agilent is available.

#### NOTES

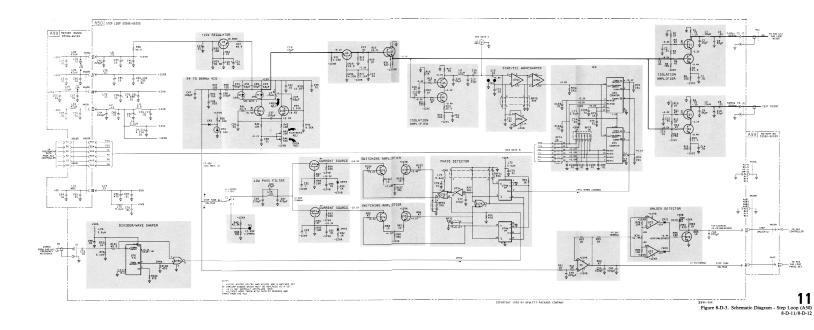

- If S1 is switched to TEST, the VCO frequency should be 54 MHz (± 0.1 MHz).

- If S1 is switched to TEST and TP1 is grounded, the VCO frequency should be approximately 77 MHz.

- 3. If TP2 is shorted to ground, the 2 MHz output from the counters (U71/U72) should go to zero. The 2 MHz reference from U75(3) may then be followed through the Phase Detector (Paragraph 8-D-19, steps 10 through 13).

- 4. If TP2 is shorted to ground, the unlock circuit should drive negative at the detector (U73/Q70) and DS70 should light.

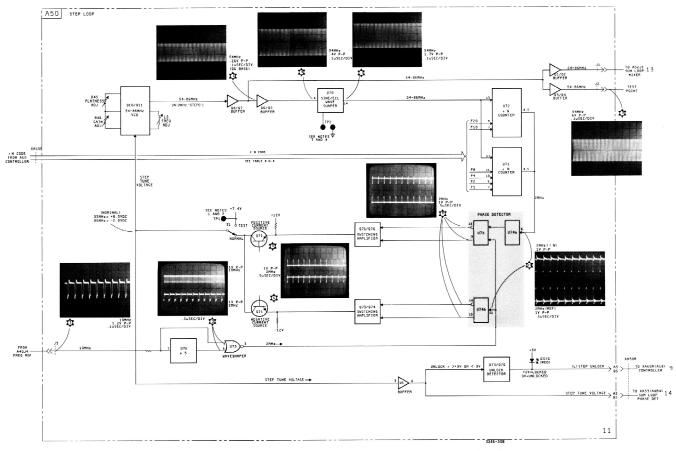

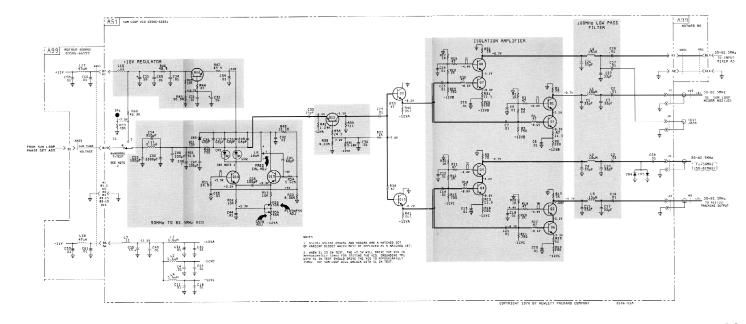

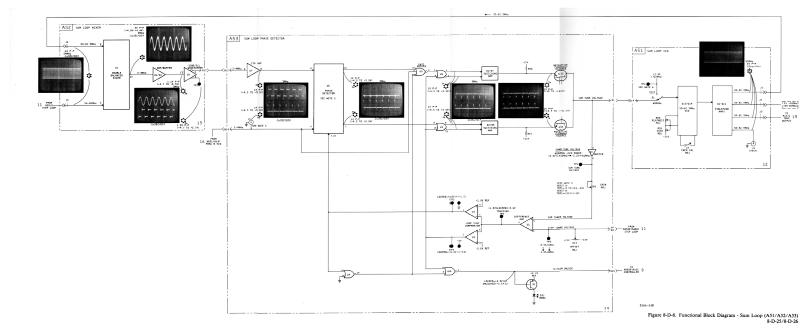

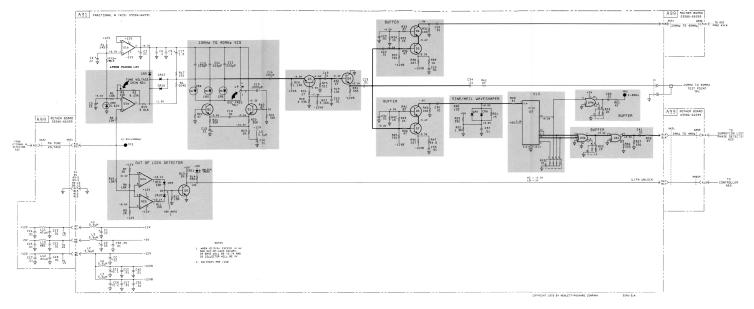

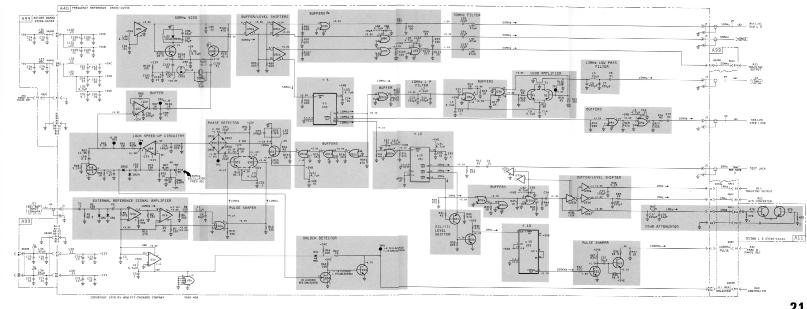

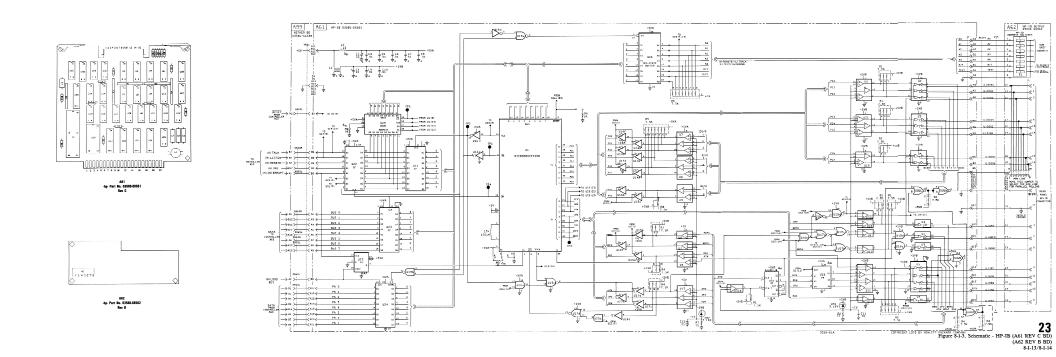

Figure 8-D-4. Functional Block Diagram - Step Loop (A50) 8-D-13/8-D-14

Model 3586A/B/C Service Group D

#### 8-D-25. Breaking The Sum Loop.

8-D-26. If the frequency at XA53(B14) is correct and that at XA53(B12) is incorrect, the problem is in the sum loop. Use the following procedure to break the sum loop for troubleshooting.

- 1. Place A51 on an extender board and set A51S<sub>1</sub> to TEST. Put a frequency counter on A51J2. The Sum VCO frequency at A51J2 should be 52MHz (±.1MHz).

- 2. If it is not 52MHz, check A51J1 and A51J3 to eliminate the Isolation Amplifiers. If it is not 52MHz at any of the outputs and TP1 is about +7.5V, the problem is in the VCO or in Q11. There is no simple way to identify a defective VCO component. Gain what information you can from schematic voltages (Figure 8-D-5) and then replace the VCO active components, one-at-a-time, until the bad component is found.

- 3. If the loop locks up with S1 in TEST at 52MHz, short A51TP1 to ground. The loop should now lock up at about 75MHz. This allows a look at a frequency other than the TEST frequency. Applying a DC source to A51TP1 (between +8V to -8V) should vary the VCO frequency between 50MHz and at least 82MHz (probably closer to 100MHz) for additional checks. (Remove the short first.)

## ECAUTION 3

If a problem exists in the VCO circuit, driving A51TP1 with too much current from a DC source could destroy additional circuit components.

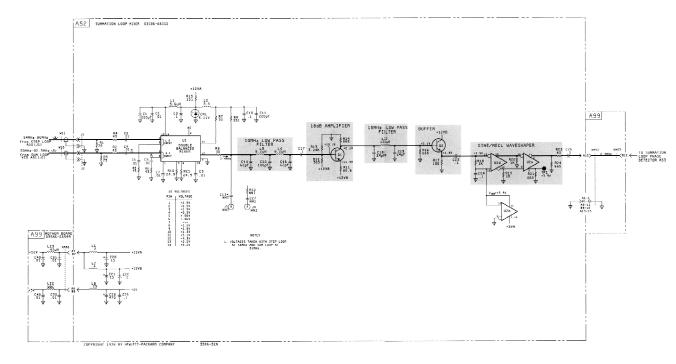

- 4. If the VCO is working, leave A51S1 in TEST to check the Sum Mixer (A52). Place A52 on an extender. With the tuned frequency at 1MHz, verify the Step VCO input at A52J1 is 54MHz and the Sum VCO input at A52J2 is about 52MHz (TEST frequency). Next check that the mixer output at XA52(A12) is about 2MHz (Step VCO minus Sum VCO). If not, the problem is on A52. Use a scope and Figure 8-D-8 to isolate to a stage on A52.

- 5. Another way to check A52, if the Sum VCO is not working even in TEST, is to jumper the 50MHz reference from A40J6 to A52J2. If the front panel is tuned to 1MHz, the Step VCO should be 54MHz and the Mixer output should be 4MHz (54-50MHz). If the tuned frequency is then changed to ØHz, CARRIER Measurement mode selected, ENTRY FREQUENCY = TONE, and (USB) CHANNEL selected, the Step VCO will change to 52MHz and the Mixer output should be 2MHz (52-50MHz).

- 6. If the mixer output is correct, place A53 on an extender board. Change the tuned frequency on the front panel to 1,999,999Hz. Check that the Fractional-N input to A53 at A53J1 is 2,000,001Hz. If yes, and the A52 mixer output of about 2MHz is also present at XA53(B12), the problem is on A53.

- 7. If the Fractional-N input at A53J1 is not correct, pull out the A31 board from the instrument. Next, remove the coax cable from A2J3 and A5J1. Connect the coax from A40J2 to A53J1. This will provide the 2MHz frequency reference from A40 as a substitute for the Fractional-N input to the Sum phase detector. Place A51S1 back in NORMAL. If the Sum Loop now locks up by itself at 52MHz as indicated by 2MHz present at XA53(B12) and extinguishing of the Sum "unlock" LED (A53DS1), then the problem is in the Fractional-N

Service Group D Model 3586A/B/C

loop. Proceed to Service Group E and continue troubleshooting. If not, then two separate problems exist, one in the Fractional-N loop and one on the A53 board. Proceed to Service Group E to troubleshoot the Fractional-N problem or continue in step 8 for the A53 problem.

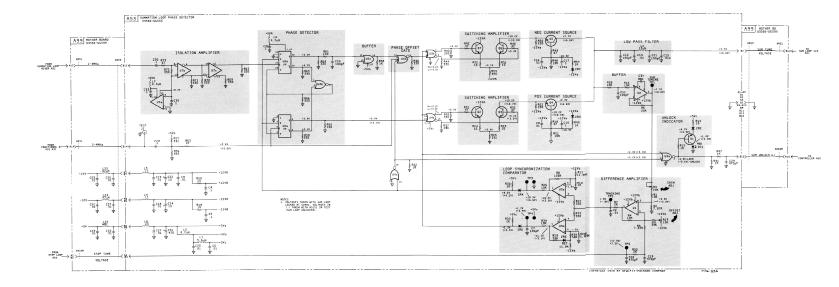

- 8. If the FN input is good and the input from the Sum Mixer is good, but A53DS1 is lit (Sum loop unlocked), remove A53U6 from its socket and ground A53TP2. With U6 removed (killing the 2MHz from A52), the SUM TUNING VOLTAGE at XA53(B2) should drive to about -11V and the Sum VCO frequency (A51S1 in NORMAL) should drive to around 95MHz. If it doesn't, check for the presence of the FN 2MHz at U5(2) and U5(3). If it's there, Q5, Q6, or Q7 are probably bad. If missing, U3, U4, or U5 are probably bad.

- 9. If the voltage at XA53(B2) is correct (about -11V), check TP1. If it's not about -10V then U2 or U1 are probably bad. Replace U6 in its socket.

- 10. The remaining potential problem area on A53 involves U1 and U3. To check the comparator outputs to the loop, proceed as follows. Short TP2 to ground. Now short the two pins of TP3 together. This should turn off the Phase Detector by setting the D input LOW. U6(14) and U6(3) should be HIGH (+4.3V). U6(15) and U6(2) should be LOW (+3.3V). The NEGATIVE current source (Q5) should be on and the POSITIVE current source (Q4) should be off. Q2 and Q6 should be off. Q3 and Q7 should be on. The SUM TUNING VOLTAGE at XA53(B2) should be full negative (about -11.7V) and the Sum VCO should be at about 96MHz (A51S1 in NORMAL). DS1 should be lit.

- 11. Remove the short from TP3. Short the two pins of TP4 together. The following conditions should now exist. U6(15) and U6(3) should be HIGH. U6(14) and U6(2) should be LOW. The POSITIVE current source (Q4) should be on and the NEGATIVE current source (Q5) should be off. Q2 and Q6 should be on. Q3 and Q7 should be off. The SUM TUNING VOLTAGE should be full positive (about +11.4V) and the Sum VCO should be at about 36MHz. DS1 should be lit.

- 12. If the conditions in both step 10 and step 11 are correct, then U1 or U3 are probably bad. Remove the shorts from TP2 and TP4. Connect a DC source to TP2. When the voltage at TP2 is held between +1.8V and -.6V, DS1 should not be lit. If it is, U3 is probably bad. Changing the voltage at TP2 above +1.8V or below -.6V should cause the comparators to trip and DS1 to be lit. If they do not, U3 is probably bad. If U3 works correctly, the problem must be U1 bad.

#### 8-D-27. Sum Loop Hints.

- 8-D-28. If the regulated +10V on A51 is higher than +10V and the SUM TUNING VOLTAGE is higher than +10V, the regulator might be good. Put A51S1 in TEST to force the tuning voltage to +7.5V. If the regulated +10V drops to +10V, the regulator is operating normally.

- 8-D-29. When the Sum loop is malfunctioning and a good First L.O. signal is needed to test other parts of the instrument, it is possible to provide a temporary substitute First L.O. Lift one end of A51L6 and inject a variable frequency source from 50-82.5MHz directly into A51J4. Set the source amplitude to -40dBm (75 ohm output impedance). With a second source into the front end (A1) and a counter on the Second I.F. test jack (15.625KHz-IFTP) on A10, the whole frequency conversion section of the receiver can be exercised. Use a full

Model 3586A/B/C Service Group D

scale input signal to A1 and be sure all your test instruments are phase locked together for accurate frequency measurements.

8-D-30. A53 Adjustment Note. When adjusting A53R3 (GAIN) and A53R13 (OFFSET), be sure to monitor the Sum VCO frequency. The loop can be locked up to the wrong frequency with these adjustments. Follow the procedures in paragraph 5-6 carefully, remembering that the Sum VCO should be equal to the front panel tuned frequency (plus 50MHz) in LO DIST or LO NOISE.

#### 8-D-31. Post-Repair Adjustments (A50/A51/A52/A53).

8-D-32. After any repairs to the current sources, current switches, or Sum/Step VCO's, check for the presence of spurs (paragraphs 4-37 and 4-39).

8-D-33. After replacement of the matched set of VARICAP tuning diodes on A50 and A51, perform all Sum and Step Loop adjustment procedures (paragraph 5-6).

Figure 8-D-6. Schematic Diagram - Sum Loop Mixer (A52) 8-D-21/8-D-22

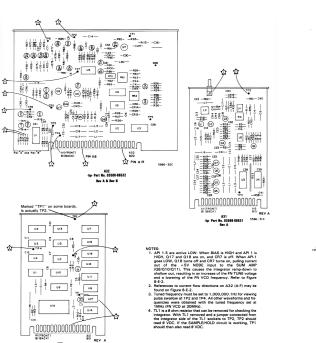

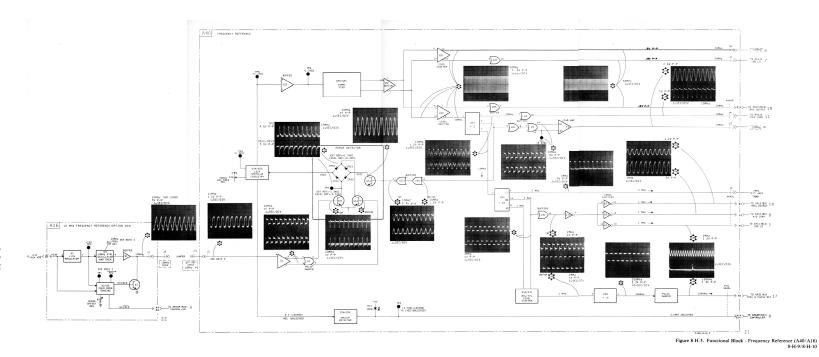

#### NOTES veforms were obtained with the front paneliert I. O. frequency in them 5.1 MHz (SUR

- ned to 1 MHz. The First L.O. frequency is then 51 MHz (SUM CO output) and the Step Loop VCO frequency is 54 MHz. The to signate entering phase detector A53U6 should therefore be 3 Hz (54-51).

- AS3J1 for test purposes with A31 removed. Refer to Paragrap 8-0-26, step 7, for information.

- Test A: With A53TP2 shorted to ground and a jumper across the dual pins of A53TP3, A53TP1 should be -9.7v (+1,

- Test 8: With A53TP2 shorted to ground and a jumper across the dual pins of A53TP4, A53TP1 should be + 11.0v (± 1v).

- A53U6 is in a socket for easy removal during trouble shooting. This allows signal tracing of the FN 2-4 MHz signal Refer to paragraph 8-D-26, step 8, for information.

- With A51S1 in TEST, the SUM VCO should be 52 MH

(± 0.1 MHz). If A51TP1 is then grounded, the SUM VCO should

#### **Table of Contents**

| Paragraph | ı                                 | Page  |

|-----------|-----------------------------------|-------|

| 8-E-1.    | Adjustments (Cross Reference)     | 8-E-1 |

| 8-E-2.    | FN VCO Adjustments (A31)          | 8-E-1 |

| 8-E-3.    | FN Phase Detector Adjustments     |       |

|           | (A32)                             | 8-E-1 |

| 8-E-4.    | Theory of Operation (Cross        |       |

|           | Reference)                        | 8-E-1 |

| 8-E-5.    | Fractional-N Loop -               |       |

|           | Paragraph 8-222                   | 8-E-1 |

| 8-E-6.    | Fractional-N VCO (A31) -          |       |

|           | Paragraph 8-224                   | 8-E-1 |

| 8-E-7.    | Fractional-N Phase Detector (A32) | ) -   |

|           | Paragraph 8-226                   | 8-E-1 |

| 8-E-8.    | Fractional-N $\div$ N (A30) -     |       |

|           | Paragraph 8-233                   | 8-E-1 |

| 8-E-9.    | Troubleshooting Data              | 8-E-2 |

| 8-E-10.   | Verifying a Fractional-N          |       |

|           | Problem                           | 8-E-2 |

| 8-E-12.   | Error Code E3.4                   | 8-E-2 |

| 8-E-15.   | FN Loop Locked at Wrong           |       |

|           | Frequency                         | 8-E-3 |

| 8-E-17.   | Breaking the Fractional-N Loop    |       |

| 8-E-19.   | Fractional-N Troubleshooting      |       |

|           | Hints                             | 8-E-5 |

|           |                                   |       |

Model 3586A/B/C Service Group E

### FRACTIONAL-N SERVICE GROUP E

#### Contents

| Adjustments (Cross Reference)         | Paragraph 8-E-1 |

|---------------------------------------|-----------------|

| Theory of Operation (Cross Reference) | Paragraph 8-E-4 |

| Troubleshooting Data                  | Paragraph 8-E-9 |

| Schematic Diagrams                    |                 |

| Fractional-N $\div$ N (A30)           | Figure 8-E-3    |

| Fractional-N VCO (A31)                | Figure 8-E-4    |

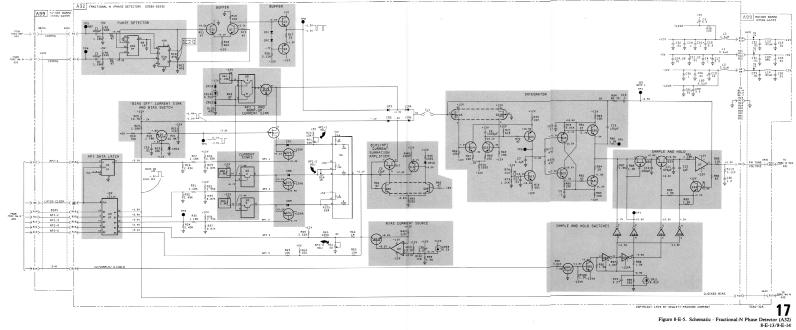

| Fractional-N Phase Detector (A32)     | Figure 8-E-5    |

| Functional Block Diagram              |                 |

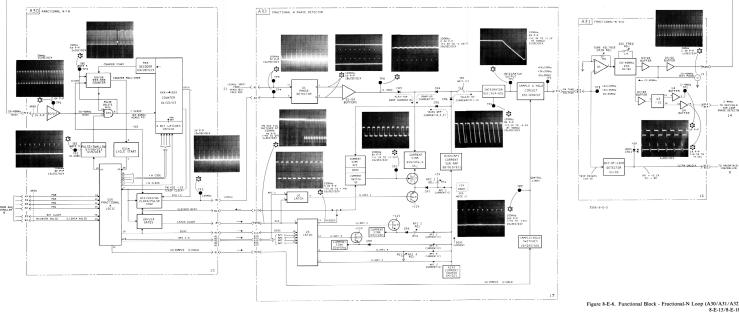

| Fractional-N Loop                     | Figure 8-E-6    |

#### 8-E-1. ADJUSTMENTS (CROSS REFERENCE).

#### 8-E-2. FN VCO Adjustments (A31).

| Designation | Adjustment Title            | <u>Paragraph</u> |  |  |

|-------------|-----------------------------|------------------|--|--|

| A31L4       | Oscillator Frequency Adjust | 5-5              |  |  |

| A31R4       | Tune Voltage Gain Adjust    | 5-5              |  |  |

#### 8-E-3. FN Phase Detector Adjustments (A32).

| Designation | Adjustment Title | Paragraph |  |  |

|-------------|------------------|-----------|--|--|

| A32R51      | API-1 Adjust     | 5-5       |  |  |

| A32R54      | API-2 Adjust     | 5-5       |  |  |

| A32R61      | API-4 Adjust     | 5-5       |  |  |

#### 8-E-4. THEORY OF OPERATION (CROSS REFERENCE).

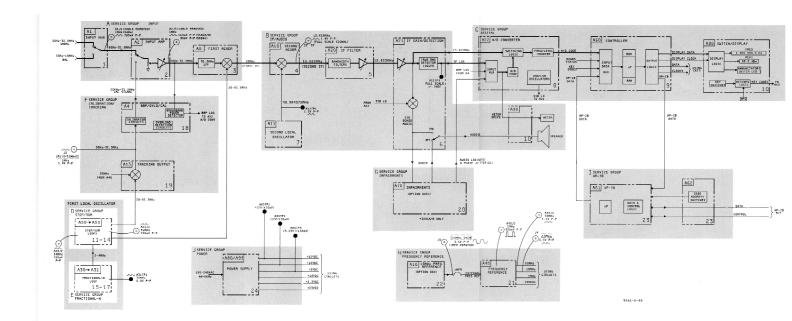

- 8-E-5. Fractional-N Loop Paragraph 8-222.

- 8-E-6. Fractional-N VCO (A31) Paragraph 8-224.

- 8-E-7. Fractional-N Phase Detector (A32) Paragraph 8-226.

- 8-E-8. Fractional-N ÷ N (A30) Paragraph 8-233.

Service Group E Model 3586A/B/C

#### 8-E-9. TROUBLESHOOTING DATA.

#### 8-E-10. Verifying a Fractional-N Problem.

8-E-11. Before attempting to troubleshoot the Fractional-N loop, verify that a problem does exist as follows.

- 1. Place A31 board on an extender card.

- 2. Connect a frequency counter to XA31(A14).

- 3. Apply power to the 3586 or press RECALL and Ø to establish turn-on conditions.

- 4. Tune the 3586 to each one of the frequency values in Table 8-E-1, verifying the FN VCO ( $\div$ 10) frequency at XA31(A14). If all frequency read outs on the counter are correct for the tuned frequencies in the table, proceed with step 5. If any of the frequency readouts are incorrect, proceed to paragraph 8-E-15.

- 5. If the frequencies at XA31(A14) are correct per Table 8-E-1, connect a scope to XA31(A14). The signal at that point should be about 1Vp-p around a zero reference, and should be a pulse about 15 to 30 nanoseconds wide (pulse width depends on frequency). If not, troubleshoot A31 using Figure 8-E-6 and Figure 8-E-4.

- 6. If the frequency, waveform and amplitude are all correct at XA31(A14) for the values in Table 8-E-1, the Fractional-N loop is working correctly. Proceed to Service Group D and troubleshoot the Step and Sum Loops if the First L.O. signal is the incorrect frequency.

#### 8-E-12. Error Code E3.4.

8-E-13. Whenever error code E3.4 is displayed on the front panel, it indicates that an "unlock" condition exists for the FN loop. Determination of unlock is made by a detector circuit (U2/Q9) which checks the FN TUNE voltage continuously to see if it is greater than +8.6V or less than -8.6V. If yes, one-half of U2 trips high, turning on Q9 and sending a (L) FN UNLOCK signal to the processor which displays the error code.

Table 8-E-1. FN Codes and Frequencies.

|                 | FN VCO       |               | l    |       |        | Cou   | nter P | reset C | ode ( | +N Nin | es Co | mpleme | ent)   |         |      | Decima |

|-----------------|--------------|---------------|------|-------|--------|-------|--------|---------|-------|--------|-------|--------|--------|---------|------|--------|

| Front Panel     | Frequency    | FN VCO +10    | ÷N   | U     | 1 Pin: | (MSD  | )      |         | U2    | Pins   |       | U      | 13 Pin | s (LSD) | )    | Preset |

| Tuned Frequency | at A31TP1    | at XA31 (A14) | Code | 11(D) | 3(C)   | 10(B) | 4(A)   | 11(D)   | 3(C)  | 10(B)  | 4(A)  | 11(D)  | 3(C)   | 10(B)   | 4(A) | Code   |

| 1,000,000.0Hz   | 30,000,000Hz | 3,000,000.0Hz | 300  | 0     | 1      | 1     | 0      | 1       | 0     | 0      | 1     | 1      | 0      | 0       | 1    | 699    |

| 1,000,000.1Hz   | 29,999,999Hz | 2,999,999.9Hz | 299  | 0     | 1      | 1     | 1      | 0       | 0     | 0      | 0     | 0      | 0      | 0       | 0    | 700    |

| 1,111,111.2Hz   | 28,888,888Hz | 2,888,888.8Hz | 288  | 0     | 1      | 1     | 1      | 0       | 0     | 0      | 1     | 0      | 0      | 0       | 1    | 711    |

| 1,222,222.3Hz   | 27,777,777Hz | 2,777,777.7Hz | 277  | 0     | 1      | 1     | 1      | 0       | 0     | 1      | 0     | 0      | 0      | 1       | 0    | 722    |

| 1,333,333.4Hz   | 26,666,666Hz | 2,666,666.6Hz | 266  | 0     | 1      | 1     | 1      | 0       | 0     | 1      | 1     | 0      | 0      | 1       | 1    | 733    |

| 1,444,444.5Hz   | 25,555,555Hz | 2,555,555.5Hz | 255  | 0     | 1      | 1     | 1      | 0       | 1     | 0      | 0     | 0      | 1      | 0       | 0    | 744    |

| 1,555,555.6Hz   | 24,444,444Hz | 2,444,444.4Hz | 244  | 0     | 1      | 1     | 1      | 0       | 1     | 0      | 1     | 0      | 1      | 0       | 1    | 755    |

| 1,666,666.7Hz   | 23,333,333Hz | 2,333,333.3Hz | 233  | 0     | 1      | 1     | 1      | 0       | 1     | 1      | 0     | 0      | 1      | 1       | 0    | 766    |

| 1,777,777.8Hz   | 22,222,222Hz | 2,222,222.2Hz | 222  | 0     | 1      | 1     | 1      | 0       | 1     | 1      | 1     | 0      | 1      | 1       | 1    | 777    |

| 1,888,888.9Hz   | 21,111,111Hz | 2,111,111.1Hz | 211  | 0     | 1      | 1     | 1      | 1       | 0     | 0      | 0     | 1      | 0      | 0       | 0    | 788    |

| 2,000,000.0Hz   | 40,000,000Hz | 4,000,000.0Hz | 400  | 0     | 1      | 0     | 1      | 1       | 0     | 0      | 1     | 1      | 0      | 0       | 1    | 599    |

Notes: 1. 0 = +0.2 VDC1 = +4.4 VDC

2. The table values shown will repeat for every 2MHz increment that is added to the Front Panel Tuned Frequency.

Model 3586A/B/C Service Group E

8-E-14. If E3.4 is displayed, check the FN TUNE voltage at A31TP3. It should always be between  $\emptyset V$  (FN VCO at 40MHz) and +6V (FN VCO at 20MHz). If it is between  $\emptyset V$  and +6V, U2 or Q9 are probably bad. If the FN TUNE voltage is >+8.6V or <-8.6V, proceed to paragraph 8-E-17.

#### 8-E-15. FN Loop Locked at Wrong Frequency.

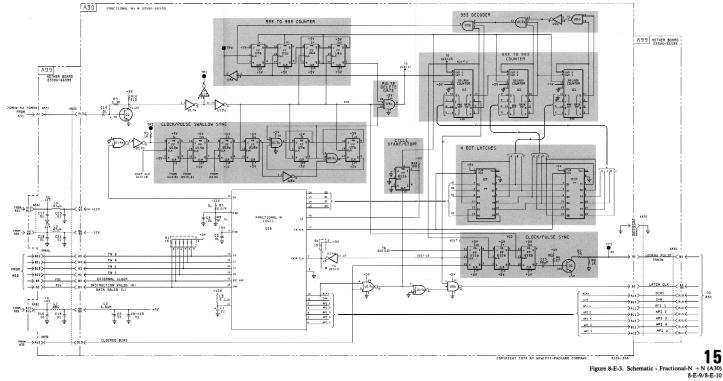

8-E-16. If the FN Loop is locked up (no error code E3.4 displayed), but the incorrect frequency is present at XA31(A14), at TP2, or at A31TP1 per Table 8-E-1, it is possible that the incorrect ÷ N code is being received at the FN Logic Chip (A30U16) from the processor Proceed as follows.

- 1. Place A30 on an extender board.

- 2. Press RECALL and Ø to restore turn-on conditions.

- 3. Check the voltage at U16 pins 20-23. They should all be about +0.3V (LOW).

- 4. Connect a scope to each pin (20 through 23) of U16, one-at-a-time, while commanding a frequency change using the FREQ STEP function of the RPG (FREQUENCY TUNE knob). You should be able to see the new  $\div$  N codes from the A60 processor causing very short pulses ( $< .1\mu$ S) on each line *only* while turning the RPG knob. You may have to turn your sweep intensity up high and your sweep speed down very slow on your scope to see the pulses because of their narrow width. A pulse-catcher of some sort may also be used.

- 5. If the pulses from A60 are not present at the input to A30U16, proceed to Service Group C and troubleshoot A60. If they are present, check to see if the correct  $\div$  N code is getting to the decade counters (U1, U2, U3) as follows.

- 6. Press RECALL and 0. Tune the 3586 to each one of the frequency values in Table 8-E-1 and check the BCD code at the preset input to U1 (MSD), U2, and U3 (LSD). If the problem appears to be frequency-related, it is best to check all of the frequency codes in Table 8-E-1 as this sometimes can isolate the problem to a particular line or to a couple of components. If all frequencies are bad, only one or two codes need to be checked to see if the preset data is getting to the decade counters at all.

- 7. If the correct code is not showing up at the decade counters, suspect U9, U10 and U16. Using the RPG as in Step 4, check for the output lines of U16 (pins 13-16) to be pulsing.

- 8. If the correct codes are getting to the decade counters, use standard digital troubleshooting techniques to check the clocks, inputs and outputs of the flip-flops, gates, and decade counters until the bad IC chip is found. Follow the VCO input through the board and use Figure 8-E-6 to verify signal flow and waveshapes where possible.

#### 8-E-17. Breaking The Fractional-N Loop.

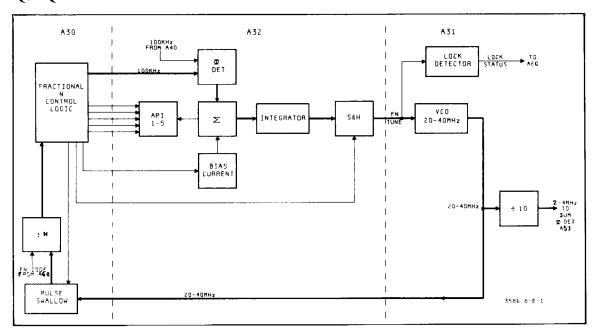

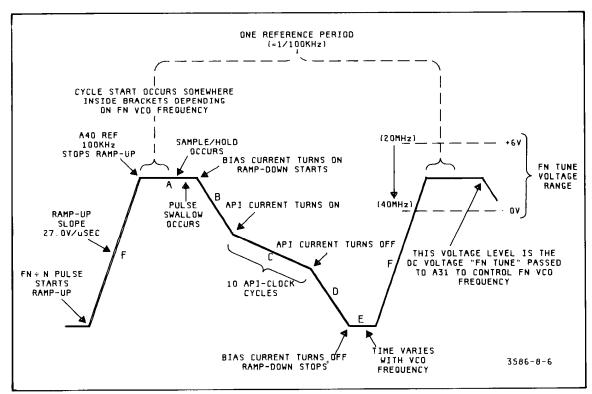

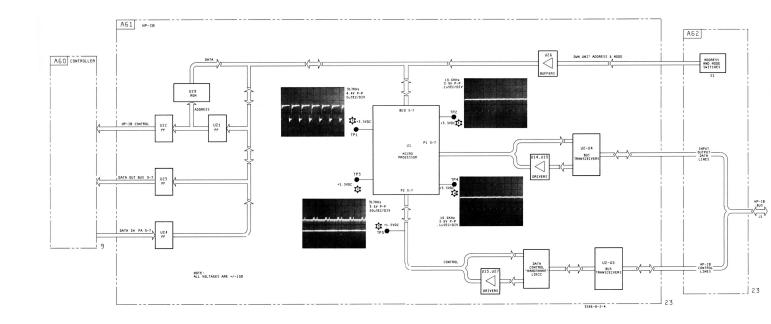

- 8-E-18. As in all phase-locked loops, the first troubleshooting step is to verify VCO operation. Then work your way around the loop (Figure 8-E-1) until the problem is isolated. Proceed as follows.

- 1. Place A31 on an extender board and short A31TP3 to ground. This should cause the VCO to oscillate at about 40MHz (A31TP1). If it does not, the VCO has a problem. Check

Service Group E Model 3586A/B/C

- U1(1) for about -8V to -9V with TP3 shorted. If present, U1 is probably good.

- 2. If the oscillator is not running at all with TP3 shorted, suspect CR4-CR6, Q1 and Q2 first. Make sure Q3 is not shorted. Make what measurements you can from the schematic (Figure 8-E-4) and then replace the active components one-at-a-time until the bad component is found. Q1 and Q2 should be on at all times.

- 3. If the oscillator is running, leave TP3 shorted and check all of the A31 board outputs using a scope. If absent from any one output, trace the signal backwards until the bad stage is found.

- 4. If the VCO output to the A30 board is present and at the correct frequency (about 40MHz with TP3 shorted), the A31 board is probably working correctly. Removing the short to ground and jumping A31TP3 to the +5V supply at either end of L3 should yield another test frequency from the FN VCO of about 22 MHz.

- 5. Place A30 on an extender board and verify the VCO input at A30TP1 is about 40MHz with A31TP3 shorted to ground. If present, tune the 3586 to 2MHz and then check A30TP3 for the presence of a 100kHz, very narrow pulse signal at about 2Vp-p. If present, the A30 board is probably good. Proceed to step 7.

- 6. If the 100kHz pulse is missing at A30TP3, follow the steps in paragraph 8-E-16 to check out the A30 board.

- 7. If the 100kHz pulse is present at A30TP3, put A30 and A31 back in their slots and place A32 on an extender board. Leave the short on A31TP3.

- 8. The best tool for troubleshooting the A32 Fractional-N Phase Detector board is a good understanding of how the board functions. If time permits, read the theory of operation for A32 in paragraph 8-226.

- 9. Check the two 100kHz inputs to A32 at TP3 and TP4. If the signal at TP3 is missing, proceed to Service Group H and troubleshoot the 100kHz output from the A40 board. If A30TP3 had the  $FN \div N$  100kHz signal present, A32TP4 should have it also.

- 10. Next check TP8 for a 100 kHz signal as shown in Figure 8-E-6. This signal will be unstable with the loop unlocked but should be present and at the correct DC level (+1.3V to -1.0V) as seen on a scope. The same is true for the other waveforms shown on Figure 8-E-6 which are phase detector-related. They are unstable with the loop unlocked, and some may have different levels than those shown. However, if 100 kHz signals are present at TP3 and TP4, the signals at TP8, TP6, and TP2 should be present. Their absence indicates a problem in that general area or preceeding it.

- 11. The LATCH CLOCK (XA32(A8)), BIAS (TP5), and S + H(TP7) signals should always be present as shown and should be stable. API 1-5 should always have a stable 100kHz pulse at 5Vp-p (+5V to  $\emptyset$ V) present at the outputs of latches U2 and U3. If any of the signals mentioned in this step are missing, trace them back to their common source (A30U16).

- 12. Press RECALL and Ø. Connect the scope to A32TP2 (the Integrator output). The signal there should resemble that shown on Figure 8-E-6. Activate the FREQ STEP function of the RPG. Changing the tuned frequency by a few Hertz with the RPG should cause the

Model 3586A/B/C Service Group E

ramp-down slope to vary. If it does, basic API current sink operation is working. This indicates that the FN Logic chip (A30U16) is functional and is sending commands to A32.

- 13. Using the FREQ STEP key in the ENTRY key group, change the Frequency Step to 100kHz. Again using the RPG, vary the tuned frequency from 0Hz to 2MHz while observing the scope connected to TP2. The width of the top flat portion of the integrator output signal should smoothly narrow from approximately 6 microseconds at 0Hz to about 3 microseconds at 1.9MHz and then jump back to 6 microseconds at 2MHz. This sequence should repeat smoothly over each 2MHz segment increment from 2MHz to 32MHz. If it does, then the integrator, the phase detector, the latches, the Bias current circuits, and the overall timing of signals from A30U16 are probably correct.

- 14. Next, check the FN TUNE voltage at A32TP1. It should agree with the DC level on the scope for the top of the ramp on the integrator output signal at A32TP2. If not, the problem is probably in the Sample/Hold Circuit. If the 100kHz pulse at TP7 is present, suspect Q32-Q34 and U7.

Figure 8-E-1. Fractional-N Loop (Simplified).

#### 8-E-19. Fractional-N Troubleshooting Hints.

- 8-E-20. As mentioned in a preceding paragraph, the best tool for troubleshooting the Fractional-N loop is a good understanding of how it works. The service technician who has never seen a Fractional-N circuit before should read all of the theory in paragraphs 8-222 through 8-243 before attempting to troubleshoot the loop. Study Figure 8-E-2 and 8-E-6 until a good understanding of functional operation is obtained and then follow the procedure in paragraph 8-E-10 to verify the problem. Review the following hints for additional information that may be of some help.

- 1. To check the API's, scope the indicated points in Table 8-E-2 while varying the frequency about 2MHz (at the indicated Frequency Step) with the RPG. Use a sweep speed of about  $2\mu$ SEC/DIV. You should be able to clearly see the narrow API pulses (0-9) in between the wider 100kHz pulses switching in number as the frequency changes. If so, that API is probably working correctly.

Service Group E Model 3586A/B/C

Table 8-E-2. API Test Points.

| API | Test Point | Freq Step | Amplitude |

|-----|------------|-----------|-----------|

| 1   | Q18(E)     | 1kHz      | 1.5Vp-p   |

| 2   | Q19(E)     | 100 Hz    | 1.0Vp-p   |

| 3   | Q20(E)     | 10 Hz     | 1.0Vp-p   |

| 4   | U3(5)      | 1 Hz      | 3.5Vp-p   |

| 5   | U3(12)     | .1 Hz     | 5.0Vp-p   |

- 2. To check the Unlock Detector on A31 quickly, ground A31TP3. The (L) FN UNLOCK line should be HIGH and LED A31CR11 should be dark. Remove the ground and jumper A31TP3 to either side of L1 (+12V). (L) FN UNLOCK should now be LOW and CR11 should be lit. Move the jumper from L1 to L2 (-12V). (L) FN UNLOCK should again be LOW and CR11 should be lit. Remove the jumper.

- 3. If the FN VCO oscillates at some frequencies but not others, suspect A31CR4-CR6.

- 4. Spurious signals at 100kHz coming from the Fractional-N could be caused by a leaky diode A32CR3-CR6. Lift one end of each and check for at least 1 Megohm. Make sure they're not open either. Other spurs are possible from out-of-tolerance resistors in U6 although field failures of that precision resistor network are unlikely.

- 5. For problems that are difficult to isolate, check that the +5V summing node at Q11(s) or U6(2) really is about +5.2V. If not, suspect Q8, Q10, Q11 and Q21.

- 6. The A32 board is more sensitive than the average board to surface contamination because of the precision currents used to control the FN VCO frequency. Corrosion buildup due to long periods of high humidity, dirt, etc. can cause unusual spurs and unstable operation of the FN Loop. After washing boards to remove dirt, inspect A32 for particles knocked loose which might wedge between IC pins, etc.

- 7. To check the integrator amplifier operation on A32, lift one end of TL1 at the input to Q22A and jumper Q22A (gate) to TP2. If the amplifier is good, Q30(E) should be ØV. If Sample/Hold is working, TP1 should also have ØV. Replace TL1.

- 8. If the integrator output at A32TP2 is stuck at the positive rail (+12V), something is pulling too much current out of the integrator input through CR4. If stuck at the negative rail (-12V), something is putting too much current into the integrator.

- 9. Always be sure the FN VCO is running as the first step to checking Fractional-N operation.

- 10. To check the phase detector circuit on A32, trigger your scope on TP3 and check TP8 for a rising edge. Then, trigger your scope on TP4 and check TP8 for a falling edge. If the indications at TP8 are correct, the phase detector is probably good.

- 11. If the FN Loop appears to be locked up at the correct frequency, but there is no 2-4MHz input on A53 from the FN loop, trace the signal forward from buffer A31Q7/Q8 to XA31(A14) until it is lost.

Model 3586A/B/C Service Group E

Figure 8-E-2. Fractional-N Integrator Output (A32TP2).

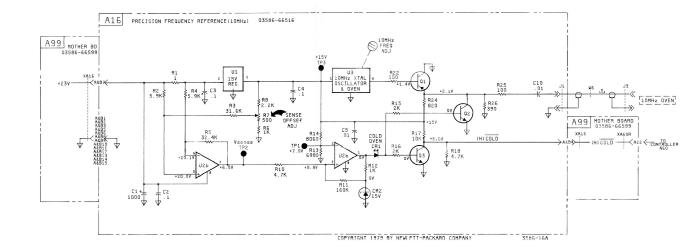

Figure 8-E-4. Schematic - Fractional-N VCO (A31) 8-E-11/8-E-12

NOTES:

1. Voltages were obtained with front penel tuned to 1MHz.

+ 2.9V at TP1 drives the FN VCO frequency to 30MHz.

#### **Table of Contents**

| Paragraph |                                | Page    |

|-----------|--------------------------------|---------|

| 8-F-1.    | Adjustments (Cross Reference)  | 8-F-1   |

| 8-F-2.    | BBP/OVLD/CAL (A4) Adjust-      |         |

|           | ments                          | 8-F-1   |

| 8-F-3.    | Tracking Output (A15) Adjust-  |         |

|           | ments                          | 8-F-1   |

| 8-F-4.    | Theory of Operation (Cross     |         |

|           | Reference)                     | 8-F-1   |

| 8-F-5.    | BBP/OVLD/CAL (A4) -            |         |

|           | Paragraph 8-183                | .8-F-1  |

| 8-F-6.    | Tracking Output (A15) -        |         |

|           | Paragraph 8-192                | .8-F-1  |

| 8-F-7.    | Troubleshooting Data           |         |

| 8-F-8.    | BBP/OVLD/CAL (A4) Trouble-     |         |

|           | shooting                       | 8-F-1   |

| 8-F-10.   | Autoranging Problems           | . 8-F-2 |

| 8-F-16.   | Broadband Power (WIDEBAND)     |         |

|           | Problems                       |         |

| 8-F-19.   | Underload/Overload Problems    |         |

| 8-F-22.   | Calibration Problems           |         |

| 8-F-27.   | A4 Troubleshooting Hints       | .8-F-5  |

| 8-F-30.   | Tracking Output (A15) Trouble- |         |

|           | shooting                       | 8-F-6   |

Model 3586A/B/C Service Group F

# CALIBRATOR, BROADBAND POWER DETECTOR AND TRACKING OUTPUT SERVICE GROUP F

#### Contents

| Adjustments (Cross Reference)         | Paragraph 8-F-1 |

|---------------------------------------|-----------------|

| Theory of Operation (Cross Reference) | Paragraph 8-F-4 |

| Troubleshooting Data                  | Paragraph 8-F-7 |

| Schematic Diagrams                    |                 |

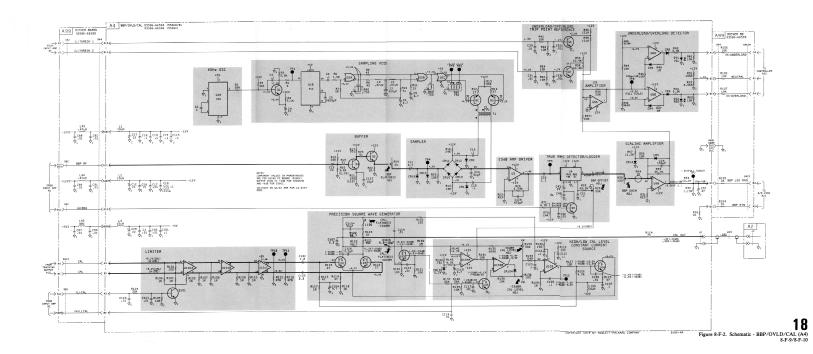

| BBP/OVLD/CAL (A4)                     | Figure 8-F-2    |

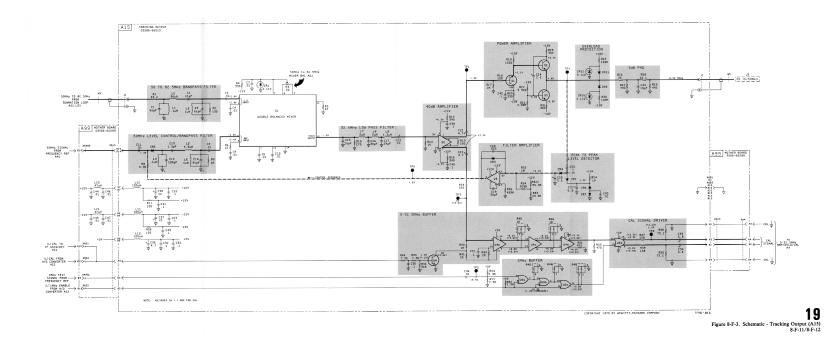

| Tracking Output (A15)                 | Figure 8-F-3    |

| Functional Block Diagrams             |                 |

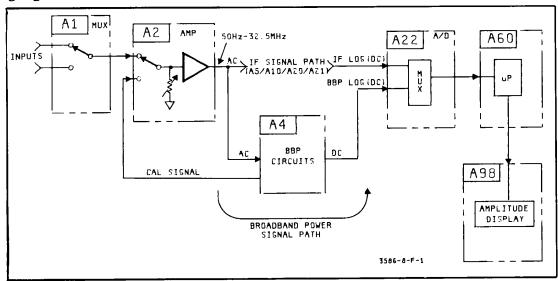

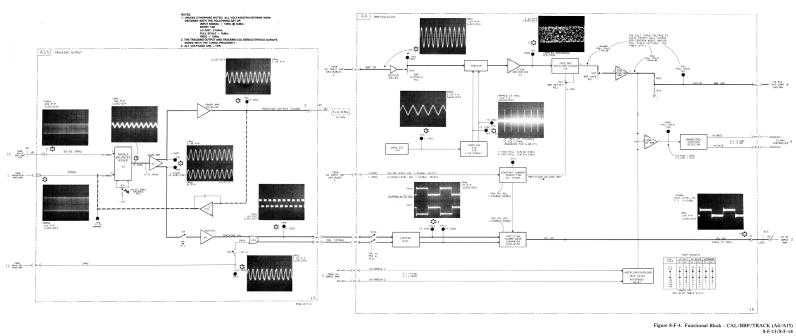

| CAL/BBP/TRACK (A4/A15)                | Figure 8-F-4    |

#### 8-F-1. ADJUSTMENTS (CROSS REFERENCE).

#### 8-F-2. BBP/OVLD/CAL (A4) Adjustments.

| Designation | Adjustment Title                     | Paragraph |  |

|-------------|--------------------------------------|-----------|--|

| A4C113      | -40dBm CAL Flatness                  | 5-20      |  |

| A4L106      | <ul><li>20dBm CAL Flatness</li></ul> | 5-20      |  |

| A4R24       | BBP Flatness Adjust                  | 5-20      |  |

| A4R29       | BBP Offset Adjust                    | 5-20      |  |

| A4R30       | BBP Gain Adjust                      | 5-20      |  |

| A4R134      | -40dBm CAL Level Adjust              | 5-20      |  |

| A4R136      | -20dBm CAL Level Adjust              | 5-20      |  |

|             |                                      |           |  |

#### 8-F-3. Tracking Output (A15) Adjustments.

| Designation | Adjustment Title     | Paragraph |

|-------------|----------------------|-----------|

| A15R3       | Mixer Balance Adjust | 5-21      |

- 8-F-4. THEORY OF OPERATION (CROSS REFERENCE).

- 8-F-5. BBP/OVLD/CAL (A4) Paragraph 8-183.

- 8-F-6. Tracking Output (A15) Paragraph 8-192.

- 8-F-7. TROUBLESHOOTING DATA.

- 8-F-8. BBP/OVLD/CAL (A4) Troubleshooting.

Service Group F Model 3586A/B/C

**8-F-9.** General. Problems related to the A4 board may include intermittent or continuous auto-ranging, WIDEBAND power amplitude measurement inaccuracies, intermittent or continuous underload or overload indications, and several different types of calibration problems. Descriptions of most of these problems together with some general procedures to follow for isolating them are contained in Table 8-9 (Troubleshooting Hints). The service technician should read all of the information under the appropriate general heading for the type of problem indicated (see paragraph 8-91). Included below are some additional hints and information.

#### 8-F-10. Auto-Ranging Problems.

- 8-F-11. In AUTO 10 or AUTO 100, the 3586 "auto-ranges" when the A60 Controller sees either the UNDERLOAD or OVERLOAD line from the A4 board go high. This signifies that the input to the True RMS Detector/Logger (A4U4) is outside the linear operating range of the chip, as sensed by the Underload/Overload Detector. In response, the processor on A60 will send a command to the A2 board to attenuate the input signal by 5dB (overload condition existing) or amplify the input by 5dB (underload condition). After the command is issued, the processor again samples the UNDERLOAD/OVERLOAD lines. If the condition still exists, another 5dB change is commanded. This sequence continues until both UNDERLOAD/OVERLOAD lines are LOW. At that time, the processor checks the IF signal amplitude and changes IF Gain up or down as required to satisfy the IF Detector/Logger circuit on A21.

- 8-F-12. If either of the UNDERLOAD/OVERLOAD lines is always HIGH, or if both lines alternate back and forth HIGH to LOW, LOW to HIGH, an auto-ranging problem exists. Possible causes include:

- 1. An unstable power level on the input signal.

- 2. Undesired amplitude modulation riding on the input signal or a second signal (undesired and unstable) present at the input.

- 3. Amplitude modulation of the input signal by the 3586, either by the A2 board or by the A4 board.

- 4. Failure of the A2 circuits to attenuate or amplify the input signal as commanded by the A60.

- 5. Failure of some circuit in the broadband power analog signal path (see Figure 8-F-1).

- 6. Failure of the Underload/Overload Detector circuit on A4.

- 7. Incorrect trip point settings for the Underload/Overload Detector.

- 8-F-13. Problems 1, 2, and 3 in paragraph 8-F-12 can usually be seen by selecting ENTRY 100 and WIDEBAND mode. If the observed signal in the MEASUREMENT/ENTRY display is "racking" continuously when it should represent a stable, pure, broadband power input signal, the problem should be either a failure of A2 or A4, or a bad input signal. Try another signal source first to eliminate that possibility. Problem 4 can be verified by forcing a CAL cycle to occur. If a CAL error code of the form CE-N (where N = 0.9, A, or b) oc-

Model 3586A/B/C Service Group F

curs, one or more of the RF Gain steps is not being selected correctly. This could be caused by a bad relay driver or a faulty relay on A2. Problem 5 requires standard signal tracing using Figure 8-F-4.

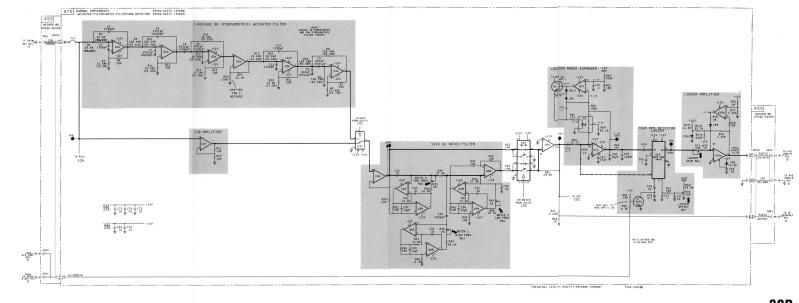

Figure 8-F-1. Broadband Power (BBP) Signal Path.

8-F-14. Problems 6 and 7 are tied together. Use Tables 8-F-1 and 8-F-2 to see if the trip points are being set correctly. Note that the voltage at TP8 should always remain constant for a Full-Scale input signal regardless of the selected mode or Full Scale setting. The different trip point settings compensate for the differing input signal levels to the Detector/Logger circuit as shown by the tables. By holding the Full Scale setting constant and by raising or lowering the level of the input signal above or below Full Scale, the actual input voltages to the Underload/Overload Detector can be monitored. It is then relatively easy to verify that the detector is working by watching the red and yellow LED's on A4, and/or monitoring the status (HIGH or LOW) of the UNDERLOAD/OVERLOAD lines to A60. Refer to the schematic (Figure 8-F-2). For example, if the input signal level is greater than the Full Scale setting, the voltage at TP8 will be less than +5.0 Volts. If the voltage drops below about +4.85V (equivalent to about +1.0dB above Full Scale), comparator U6B should trip, U6(7) should go to the positive rail and XA4 (B14) should go HIGH (about +1.8V) signaling an OVERLOAD condition to the A60 processor. If the signal level drops below full scale, when the voltage at TP8 exceeds +6.65V (about -7.5dB below Full Scale), comparator U6A should trip and XA4 (A14) should go HIGH signaling an UNDERLOAD condition to the processor.

**Full Scale**  $(\Delta 5dB)$  $(\Delta 10dB)$ **Full Scale Voltage** Trip Thresh 2 TP7 TP8 **Points** Setting Thresh 1 Mode + 5.0V OdB LO NOISE (LN) 30dBm н -.25V н -.30V+ 5.0V - 5dB LO DIST (LD) 30dBm Н 10dB .35V +5.0V(LN) and (LD) 40dBm н L -.40V + 5.0V – 15dB 45dBm L L (LN) and (LD) +5.0V 5dB н -30VWIDEBAND 30dBm

Table 8-F-1. Underload/Overload Trip Point Settings.

NOTES: 1. Voltages are ± 10%.

- 2. H = +3.8V, L = +.26V at XA4 (A13, B11).

- 3. ENTRY 100, Full Scale input signal at the tuned frequency.

- 4. See also Table 8-F-2 (Trip Point Thresholds vs. Full Scale Settings).

Service Group F Model 3586A/B/C

|                                                                                                                                                                     | ro c                      | IST   | LO NOISE |                 | WIDEBAND |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------|----------|-----------------|----------|------|

| Full Scale                                                                                                                                                          | TH 1                      | TH 2  | TH 1     | TH 2            | TH 1     | TH 2 |

| + 25<br>+ 20<br>- 30<br>- 35<br>- 40<br>- 45                                                                                                                        | H - 1 - 1 - 1 - 1 - 1 - 1 | II II | III JI J | 11 <b></b> 11-1 |          | I    |

| NOTES: 1. ENTRY 100 used to select Full Scale setting. 2. H = +3.8V, L = +.26V at XA4 (A13, B11). 3. See also Table 8-F-1 (Underload/Overload Trip Point Settings). |                           |       |          |                 |          |      |

Table 8-F-2. Trip Point Thresholds vs. Full Scale Settings.

8-F-15. It should be noted that some operational usages of the 3586 require that an input signal have amplitude modulation present. If continuous autoranging occurs in these situations, especially when low frequencies (<100Hz) or low signal levels are involved, selecting AVEraging to ON will often cure the problem. If not, the ENTRY mode of setting Full Scale

#### 8-F-16. Broadband Power (WIDEBAND) Problems.

should be used. See also "Auto-Range Problems" in Table 8-9.

8-F-17. If a discrete frequency input signal of known amplitude is applied to the input and its amplitude is correctly measured by the 3586 in LO DIST, but a large amplitude error exists in WIDEBAND, the problem could be due to one of the following causes:

- 1. A2 output buffer failure (BBP signal path).

- 2. A4 BBP signal path circuit failure.

- 3. A22 input buffer or input multiplexer failure.

8-F-18. Problems 1 and 2 in paragraph 8-F-17 can be checked by signal tracing using Figure 8-F-4. Problem 3 can be checked by monitoring the voltage at A4TP7 while varying the amplitude of the input signal. In LO DIST mode, a Full Scale signal should read -.3VDC and should change by 10 millivolts/dB as the input signal is reduced below Full Scale until, at 80dB below Full Scale, TP7 should read about -1.1VDC. If this check proves correct, the problem is most likely at the input circuits on A22.

#### 8-F-19. Underload/Overload Problems.

8-F-20. Some underload/overload condition indications are normal operation for the 3586. For example, if the manual ENTRY method of setting Full Scale has been selected by the operator, and he then inputs a signal that is too far above or below the current Full Scale setting, an overload/underload condition does exist and should be so indicated on the front Panel. See the discussion under "Overload/Underload Indications" in Table 8-9 for more detailed information.

8-F-21. For those situations which are not normal, the Underload/Overload Detector circuits can be checked using the procedure described in paragraph 8-F-14.

Model 3586A/B/C Service Group F

#### 8-F-22. Calibration Problems.

8-F-23. A detailed discussion on troubleshooting calibration problems may be found under "Calibration Problems" in Table 8-9. Other information on the CAL cycle is contained in paragraphs 8-30 and 8-32. See also Table 8-F-3 and the information in paragraphs 8-F-24 to 8-F-26.

Format is CE-N Suspect Cards Item Under CAL Where N = Ø to 9, A, b A2\* RF Gain, Step N A10, A20 С 400Hz Filter d 20Hz Fillter A20 10/100dB or WIDEBAND A21, (A4) \* \* Ε Weighted Filter A21, A22, A70\*\*\* If all RF Gain steps fail, the problem could be anywhere in the receiver circuits. Press MEAS CONT to exit the CAL cycle and run TF 13 (paragraph 8-81). If CAL is performed in WIDEBAND, the A4 BBP circuits are calibrated instead of the IF signal path through A21. \*\*\* If A60S2(2) is OPEN and an A70 Impairments board (Option 003) is not installed, CE-F will always occur during the CAL cycle.

Table 8-F-3. Calibration Error Codes.

- 8-F-24. When the CAL cycle is performed in WIDEBAND, the First L.O. frequency is automatically set to 51.23MHz by the processor so that the A15 tracking output (and therefore the calibration signal frequency) will be 1.23MHz. After the CAL cycle is finished, the First L.O. frequency is restored to whatever it was before the CAL cycle began.

- 8-F-25. When the CAL cycle is performed in LO DIST or LO NOISE, the First L.O. is automatically set to a frequency 50Hz lower than it was, for the duration of the CAL cycle. This is to allow an accurate CAL constant to be derived, free from the influence of any very strong input signal simultaneously present within the instrument (on A1). Also, if the 3586 is tuned to a frequency below 20kHz when a CAL cycle is performed, the First L.O. is automatically set to 50.020MHz for the duration of the CAL cycle so that the CAL signal frequency is 20kHz. If AVE is on when CAL occurs, it is turned off for the duration of CAL and then turned back on.

- 8-F-26. If CAL is not working at all but the 3586 appears to measure input signals correctly, the CAL signal may not be getting turned on. The (L) CAL command signal from the processor that should turn on the CAL signal goes two places. On A15, it turns off A15Q4 which allows the tracking output signal to be sent to A4 for use as the CAL signal. On A4, it turns off A4Q101 which allows A4 to accept the tracking output signal. If either A15Q4 or A4Q101 were shorted, CAL could not turn on.

#### 8-F-27. A4 Troubleshooting Hints.

8-F-28. When checking the 80Hz Oscillator and the Sampling VCO, one end of R1 ( $\emptyset\Omega$ ) may be lifted to obtain a stable sampling VCO frequency. The 80Hz Oscillator normally frequency modulates the Sampling VCO output between 20kHz and 50kHz so with R1 lifted it should oscillate somewhere in that frequency range. Also, if the 80Hz Oscillator is running

Service Group F Model 3586A/B/C

low in frequency (e.g. 60Hz), it can beat with the power line frequency causing auto-range problems. A possible auto-range problem on earlier serial number instruments might be cured by the newer component values for A4R43 and A4R45. Old values (Serials prior to 1927A-00101) were 46.4k $\Omega$  (A4R43) and 52.3k $\Omega$  (A4R45). Newer instruments may have either 53.6k $\Omega$  or 56.2k $\Omega$  for A4R43 and 56.2k $\Omega$  or 61.9k $\Omega$  or A4R45.

8-F-29. If the Calibration signal flatness needs adjusting, always adjust L106 before C113. If BBP linearity problems exist, check the Sampler circuit diodes first since the range of the Detector/Logger is more than adequate to handle frequency response. To check the Detector/Logger, lift one end of C26 and inject an A.C. signal at TP5 while measuring the D.C. output voltage of U4 at TP7. The Detector Logger should respond linearly according to Table 8-F-4. To check the Detector/Logger using an input signal, leave C26 in the circuit, select ENTRY 100, set Full Scale to ØdBm and input signals as shown in Table 8-F-4.

|         | al Relative<br>I Scale | 1     | (pk-pk)<br>P5 | Volts D.C.<br>U4(6) |         | Volts D.C.<br>TP7 |         |

|---------|------------------------|-------|---------------|---------------------|---------|-------------------|---------|

| A       | В                      | A     | В             | A                   | В       | Α                 | В       |

| + 5dBm  | + 5dBm                 | 6.0 V | 6.0 V         | + 45mV              | + 45mV  | 25V               | 25      |

| ØdBm    |                        | 3.5 V |               | + 62mV              |         | 30V               |         |

|         | - 1 dBm                |       | 3.0 V         |                     | + 65mV  |                   | 31      |

| – 5dBm  |                        | 1.9 V |               | + 79mV              |         | 35∨               |         |

|         | 7dBm                   |       | 1.5 V         |                     | +85mV   |                   | 1 – .37 |

| - 10dBm |                        | 1.1 V |               | + 95mV              |         | 40V               | -       |

|         | - 13dBm                |       | .75V          |                     | - 105mV |                   | 43      |

| - 15dBm |                        | .60V  |               | + 112mV             |         | 45V               |         |

|         | - 19dBm                |       | .38V          |                     | + 125mV |                   | 49      |

| - 20dBm |                        | .35∨  |               | + 128mV             |         | ~.50V             |         |

| - 25dBm | - 25dBm                | .19V  | .19V          | +145mV              | + 145mV | 55V               | 55      |

| - 30dBm |                        | .14V  |               | +161mV              |         | 60V               | "       |

|         | - 31dBm                |       | .10V          |                     | +165mV  |                   | 61      |

Table 8-F-4. Detector/Logger Linearity.

2. (B) readings are for 6dB steps of the input signal.

3. Voltages are calculated values and may actually be  $\pm 10\%$ .

#### 8-F-30. Tracking Output (A15) Troubleshooting.

8-F-31. Troubleshooting A15 should be a fairly straightforward operation using Figure 8-F-4. Verify the two input signals (50MHz from A40 and First L.O. from A51) are present first, then check that the mixer output frequency as seen at TP1 and TP3 is equal to the difference of the two mixer input frequencies. If the frequencies are correct but the levels are not close to the values indicated on the functional block diagram, suspect the leveling loop.

8-F-32. The tracking output signal (0-32.5MHz) at A15J2 is meant to be used by external instruments for tracking the 3586 tuned frequency. The level of this signal is normally verified to be  $0 \pm .2dBm$  at 10kHz. All other 5MHz points (from 0-30MHz) are then checked to be within  $\pm$  .25dB of the actual level noted at 10kHz. To maintain this output level close to ØdBm at all frequencies from 0 - 32.5MHz, a leveling feedback loop is used. The output signal is tapped at TP2 and its level measured by a Peak-to-Peak detector.

8-F-33. If the tracking output signal is not  $\emptyset dBm \pm 0.5dB$  from 0 - 32.5MHz, the leveling loop may be at fault. The voltages in the Peak-to-Peak detector circuit are critical for correct leveling to occur. If the loop is suspected, lift the end of R8 which connects to TP6 and connect a DC source to R8. If a DC voltage from 0 to +1V is applied to R8, it should change

Model 3586A/B/C Service Group F

the level of the 50MHz input to U1 by changing the operating impedance of CR2 (as the leveling loop is *supposed* to do). This in turn should vary the mixer output level and thus the tracking output level. If it does, suspect U3 or CR3 - CR7. If it does not affect the mixer output level, suspect mixer U1 and CR2. It is also possible for U2 to affect the tracking output flatness.

8-F-34. The CAL output portion of A15 is easily verified. A signal should not be present at TP4 unless the CAL cycle (about 3 seconds maximum), TF2 (paragraph 8-58), or TF12 (paragraph 8-79) are active. When CAL or TF2 are active, TP4 will have a 1MHz signal present. Only one signal (or neither) should be present at the input to U5D at one time, never both. The signals at U4 and U5 are all ECL levels (+4.1VDC peak to +3.2VDC base). At TP4, the signals are 160mVp-p (from +1.2VDC peak to +1.04VDC base) due to the action of R47 and R48 as a voltage divider.

8-F-35. In LO DIST and LO NOISE modes, any difference in frequency between the tracking output and the front panel tuned frequency indicates a problem. If the First L.O. frequency at A15J1 is equal to the front panel tuned frequency +50MHz, then the First L.O. is correct and the problem is probably the Mixer A15U1. If not, then the problem is somewhere in the First L.O. boards. Refer to Service Group D for procedures to troubleshoot the First L.O. signal. The tracking output may normally disagree with the front panel when the selected mode is not LO DIST or LO NOISE. See Table 8-F-5 for normal tracking output frequencies versus mode selections.

Table 8-F-5. Tracking Output Frequencies vs. Mode Selections.

| Measurement Mode Selection                        | Entry Frequency                    | Channel | Tracking Output Frequency #                                                                              |

|---------------------------------------------------|------------------------------------|---------|----------------------------------------------------------------------------------------------------------|

| LO DIST, LO NOISE, WIDEBAND                       | *                                  | *       | 1,000,000Hz                                                                                              |

| NOISE/DEMOD, NOISE/TONE,<br>PHASE JITTER, IMPULSE | CARRIER<br>CARRIER<br>TONE<br>TONE | 2772    | 1,001,850Hz<br>998,150Hz<br>999,154Hz (998,950Hz)<br>1,000,846Hz (1,001,050Hz)                           |

| TONE 1004Hz (TONE 800Hz) #                        | TONE<br>CARRIER<br>CARRIER         | ۲۷ .    | 1,000,000Hz<br>998,996Hz (999,200Hz)<br>1,001,004Hz (1,000,800Hz)                                        |

| CARRIER                                           | CARRIER<br>TONE<br>TONE            | > 7.2   | 1,000,000Hz<br>1,001,004Hz (1,000,800Hz)<br>998,996Hz (999,200Hz)                                        |

| SIGNAL 2600Hz (1010Hz) #                          | TONE<br>TONE<br>CARRIER<br>CARRIER | 2772    | 1,001,596Hz (1,000,210Hz)<br>998,404Hz (999,790Hz)<br>997,400Hz (998,990Hz)<br>1,002,600Hz (1,001,010Hz) |

NOTES: 1. All readings taken with front panel tuned frequency = 1,000,000Hz.

# Where only one frequency is given, applies to 3586A/B. Where two frequencies given, first = 3586B, second () = 3586A.

3. \* Selection has no effect on T. O. frequency.

# **Table of Contents**

| Paragraph | Page                                  |

|-----------|---------------------------------------|

| 8-G-1.    | Adjustments (Cross Reference)8-G-1    |

| 8-G-2.    | Phase Jitter Adjustments8-G-1         |

| 8-G-3.    | Notch Filter Adjustments8-G-1         |

| 8-G-4.    | Logger Adjustments8-G-1               |

| 8-G-5.    | Impulse Noise Adjustments8-G-1        |

| 8-G-6.    | Theory of Operation (Cross            |

|           | Reference) 8-G-2                      |

| 8-G-7.    | Phase Jitter8-G-2                     |

| 8-G-8.    | Weighted Filter/Notch Filter8-G-2     |

| 8-G-9.    | Impulse Noise Circuits8-G-2           |

| 8-G-10.   | Calibration Oscillator8-G-2           |

| 8-G-11.   | Troubleshooting Data8-G-2             |

| 8-G-12.   | General Information8-G-2              |

| 8-G-16.   | Phase Jitter Troubleshooting8-G-2     |

| 8-G-19.   | Phase Jitter Error Codes (E2.2,       |

|           | E2.3, E2.9)8-G-3                      |

| 8-G-23.   | Weighted Filter Troubleshooting8-G-4  |

| 8-G-26.   | Notch Filter Troubleshooting8-G-5     |

| 8-G-29.   | Audio Detector/Logger Trouble-        |

|           | shooting8-G-6                         |

| 8-G-34.   | Impulse Noise Circuit Trouble-        |

|           | shooting8-G-7                         |

| 8-G-39.   | Impulse Error Codes (E6.1, E6.2)8-G-9 |

| 8-G-42.   | Calibration Oscillator Trouble-       |

|           | shooting8-G-9                         |

# IMPAIRMENTS SERVICE GROUP G

#### Contents

| Adjustments (Cross Reference)         | Paragraph 8-G-1  |

|---------------------------------------|------------------|

| Theory of Operation (Cross Reference) | Paragraph 8-G-6  |

| Troubleshooting Data                  | Paragraph 8-G-11 |

| Schematic Diagrams (A70)              |                  |

| Phase Jitter Circuits                 | Figure 8-G-1     |

| Weighted/Notch Filters                | Figure 8-G-2     |

| Impulse Noise Circuits                | Figure 8-G-3     |

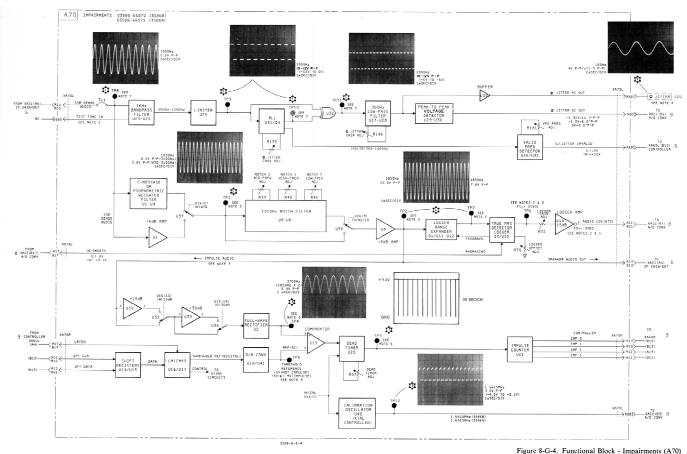

| Functional Block Diagram              | Figure 8-G-4     |

#### 8-G-1. ADJUSTMENTS (CROSS REFERENCE).

# 8-G-2. Phase Jitter Adjustments.

| Designation | Designation Adjustment Title |      |

|-------------|------------------------------|------|

| A70R181     | VFD FREQ ADJ                 | 5-22 |

| A70R146     | PHASE JITTER GAIN ADJ        | 5-22 |

| A70R133     | PHASE JITTER 20Hz ADJ        | 5-22 |

| A70R125     | PHASE JITTER 4Hz ADJ         | 5-22 |

## 8-G-3. Notch Filter Adjustments.

| <b>Designation</b> | Adjustment Title | <u>Paragraph</u> |

|--------------------|------------------|------------------|

| A70R33             | NOTCH 2          | 5-22             |

| A70R40             | NOTCH 1          | 5-22             |

| A70R45             | NOTCH 3          | 5-22             |

|                    |                  |                  |

## 8-G-4. Logger Adjustments.

| <b>Designation</b> | Adjustment Title  | Paragraph |  |

|--------------------|-------------------|-----------|--|

| A70R70             | LOGGER OFFSET ADJ | 5-22      |  |

| A70R72             | LOGGER GAIN ADJ   | 5-22      |  |

## 8-G-5. Impulse Noise Adjustments.

| Designation | Adjustment Title   | Paragraph |

|-------------|--------------------|-----------|

| A70R102     | COMPARATOR REF ADJ | 5-22      |

| A70R97      | DEAD TIMER ADJ     | 5-22      |

Service Group G Model 3586A/B/C

- 8-G-6. THEORY OF OPERATION (CROSS REFERENCE).

- 8-G-7. Phase Jitter Paragraph 8-276.

- 8-G-8. Weighted Filter/Notch Filter Paragraph 8-281.

- 8-G-9. Impulse Noise Circuits Paragraph 8-285.

- 8-G-10. Calibration Oscillator Paragraph 8-288.

- 8-G-11. TROUBLESHOOTING DATA.

- 8-G-12. General Information.

- 8-G-13. The A70 performs all of its functions (Phase Jitter measurements, Weighted/Notch Filter operation, Impulse measurements) on the SSB Demodulated audio from the A21 board. To check A70 operation, therefore, verify that a good, clean audio signal is available at the input (A70TP8) and trace it through the appropriate circuits.

- 8-G-14. To get a 1850Hz full-scale signal at TP8, perform the following steps:

- 1. On the 3586A/B, press RECALL, 0 to restore turn-on conditions.

- 2. Select ENTRY 100 and set Full Scale to ØdBm.

- 3. Input 1MHz at ØdBm. Be sure the selected termination impedance matches the signal source.

- 4. TP8 should now have a 1850Hz signal at 2.2Vp-p as seen on an oscilloscope or 0.75 VRMS as measured on a DVM.

- 8-G-15. Another method of obtaining an audio signal of the desired frequency and amplitude at A70TP8 is to disconnect all external signals, press RECALL, Ø to restore turnon conditions, activate TF12 (paragraph 8-79), and then select ENTRY 100 and a full scale setting of -40dBm. This will give you a full scale signal in to A70TP8 of 2.2Vp-p at 1850Hz. If you now selectively change the front panel turned frequency of the 3586 by a given amount (e.g., 100Hz), the signal frequency at A70TP8 will change by the same amount. Within the range of the selected bandwidth, the amplitude of the signal should stay about the same at TP8 or about 2.2Vp-p.

#### 8-G-16. Phase Jitter Troubleshooting.

8-G-17. To measure residual phase jitter, follow steps 1-3 in paragraph 8-G-14 (except input a 1.001MHz signal at  $\emptyset$ dBm) and then select  $\phi$  JITTER mode. TP8 should now have a clean 1000Hz sine wave at 2.2Vp-p. The residual phase jitter displayed on the front panel should be less than 0.5°p-p. If it is greater than 0.5°, check the waveforms at TP8, TP9, TP10, and TP11 as shown on Figure 8-G-4. If they are good, check U29(3) for  $\emptyset$  VRMS. If U29(3) is good, check U30(1) for  $\emptyset$  VDC. If U30(1) is good, the problem may be noise on the A/D board. Go to Service Group C and check all the inputs to the A/D for noise. If the signal at TP8, TP9, TP10, TP11, U29(3) or U30(1) is bad, suspect the preceding stage. If there is any doubt as to how "clean" the input signal at TP8 is when a high residual phase jitter is present, look at the signal with a spectrum analyzer for the presence of sidebands.

8-G-18. If residual phase jitter is acceptable, the following procedure will verify phase jitter operation.

- 1. Set up two sources with the same output impedance (e.g. 75 ohms) with one at 1.001MHz/0dBm and the other at 1.001150MHz/-20dBm.

- 2. Connect the two sources to the same input termination impedance (e.g., 75 ohms) on the 3586 using a power combiner (see Table 8-14, "Recommended Test Equipment").

- 3. Press RECALL, Ø to restore turn-on conditions.

- 4. Turn on counter. Display should read 1.001MHz at approximately -6dBm.

- 5. Select  $\phi$  JITTER mode.

- 6. Display should read  $+11.5^{\circ}$  ( $\pm 0.1^{\circ}$ ) p-p. If it does not, check the waveforms at TP8, TP9, and TP11. They should be as shown on Figure 8-G-4 except for some jitter (150Hz) on the rising and falling edges. There should be no jitter on the waveform at TP10, otherwise it should look the same as that on TP9 and should always track TP9 exactly in frequency.

- 7. If these points are good, check U29(3) for a 150Hz sine wave at 3.8v(p-p). The same signal should be at the  $\phi$  JITTER AC out BNC on the rear panel. If these are good, check U30(1) for -1.9vdc (= +11.5°p-p). If good, problem is on the A/D board (A22). If bad, problem is in the Peak-to-Peak Detector circuit. Note that the  $\frac{p-p}{2}$  value of the  $\phi$  JITTER AC out should equal the  $\phi$  JITTER DC output value.

#### 8-G-19. Phase Jitter Error Codes.

- 8-G-20. Error Code E 2.2 indicates that the input signal to the 3586 is 40dB or more below the current Full Scale setting and is not of sufficient level to accurately make a phase jitter measurement. This is determined by the processor taking an IF amplitude measurement from A21 and therefore has nothing to do with the status of the A70 board.

- 8-G-21. Error Code E 2.3 is an indication that the tone frequency upon which phase jitter measurements are being attempted is not within 960-1060Hz and therefore is not valid. If the tone is known to be within this range, A70R181 may need adjusting. This pot moves a 100Hz "window" all at once. For example, if the present limits for a valid signal were 900-1000Hz, adjusting A70R181 could move the window back to 960-1060Hz where it belongs. When the tone is valid, the voltage at U26(6/10) will be between that at U26(2) and U26(11). U26(4) will be LOW, U26(5) will be HIGH and U26(2) will be HIGH (valid). If the tone exceeds 1060Hz, the voltage at U26b(6) will be greater than 4.6V. This in turn, will cause U26b(1) to be LOW along with U26a(5). U26a(2) will also go LOW. If the tone goes less than 960Hz, the voltage at U26d(10) will be less than 3.5V. This causes U26(13) to go HIGH in conjunction with U26a(4). The "greater" amplitude at the negative input of U26a will cause U26a(2) to go LOW, again indicating an invalid signal. (See Section VII (Δ11).)

- 8-G-22. Error Code E 2.9 indicates that the phase jitter DC output to the A22 A/D Converter is not between  $\emptyset$  and -2.0 vdc as measured at the A/D. There is a voltage divider on A22 that reduces the output of A70U30(1) to an acceptable level for the A/D with a maximum of -2.0 vdc being equivalent to about  $40^{\circ}$ p-p of phase jitter. The A70 board is capable of measuring larger levels of phase jitter but a practical level of information is quickly exceeded past  $40^{\circ}$ p-p. Since the scale factor for the output at U30(1) is  $6^{\circ}/-1$  vdc,

Service Group G Model 3586A/B/C

the -6.67 dc at U30(1) is equivalent to 40°p-p of phase jitter. The voltage divider inputs 30% of this to the A/D (or -2.0 vdc) and if this level is exceeded, E 2.9 is displayed. A70R146 adjusts the gain of U28A so that 6° of phase jitter is equal to -1.0 vdc.

#### 8-G-23. Weighted Filter Troubleshooting.

8-G-24. To check the Weighted Filter, use the following procedure.

- 1. Perform all the steps in paragraph 8-G-14.

- 2. Connect a scope to TP1.

- 3. With 3100Hz bandwidth selected, TP1 should have the 1850Hz waveform shown there in Figure 8-G-4 with a p-p value of 4.5v which is double (or +6dB) that at TP8 (2.2v p-p Full Scale).

- 4. Select WTD 3100Hz bandwidth.

- 5. The signal level at TP1 should drop about 15% as the weighted filter is switched in. Example: 4.5v (p-p) to 3.7v (p-p). This is true only for a signal with a frequency of 1850Hz. Other frequencies will yield different results.

8-G-25. For a 3586B, a 1000Hz signal at TP1 will stay the same amplitude with the weighted filter in. For a 3586A, 800Hz at TP1 will stay about the same amplitude with weighting. Frequencies other than 800Hz or 1000Hz should get some level reduction at TP1 when the weighted filter is switched in (depending on the frequency). To vary the frequency at TP1 (and TP8), simply vary the input signal frequency or the 3586 tuned frequency as necessary to obtain the desired frequency. When the tuned and input frequencies are the same, TP1 and TP8 will have 1850Hz present in LO DISTortion mode. See Table 8-G-1 for some typical amplitude reductions (for comparison only) at different frequencies for a 3586B "C-Message" weighted filter. A 3586A "Psophometric" weighted filter would have similar values. Note that if a full-scale input signal to the 3586 does not produce a full scale audio signal (2.2Vp-p or 0.75 VRMS) at TP8, the problem is most likely **not** on A70. (See Service Group B for troubleshooting audio problems.)

Table 8-G-1. C-Message Filter Weighting.

| Input Frequency                                                                            | Weighted Signal                                                                                                            | Signal Reduction In                                                                        |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| (A70TP8)                                                                                   | Amplitude (A70TP1)                                                                                                         | dB Relative to 1KHz                                                                        |

| 400Hz<br>500Hz<br>600Hz<br>700Hz<br>800Hz<br>900Hz<br>1000Hz<br>1200Hz<br>1400Hz<br>1600Hz | 1.2V (p-p)<br>1.8V (p-p)<br>2.5V (p-p)<br>3.2V (p-p)<br>3.8V (p-p)<br>4.2V (p-p)<br>4.3V (p-p)<br>4.2V (p-p)<br>4.0V (p-p) | - 12.2dB<br>- 7.7dB<br>- 4.6dB<br>- 2.5dB<br>- 1.1dB<br>- 0.3dB<br>0<br>- 0.2dB<br>- 0.7dB |

| 1850Hz                                                                                     | 3.8V (p-p)                                                                                                                 | - 1.1dB                                                                                    |

| 1850Hz                                                                                     | 3.7V (p-p)                                                                                                                 | - 1.3dB                                                                                    |

| 2000Hz                                                                                     | 3.7V (p-p)                                                                                                                 | - 1.3dB                                                                                    |

| 2500Hz                                                                                     | 3.6V (p-p)                                                                                                                 | - 1.6dB                                                                                    |

| 3000Hz                                                                                     | 3.2V (p-p)                                                                                                                 | - 2.8dB                                                                                    |

| 3100Hz                                                                                     | 2.9V (p-p)                                                                                                                 | - 3.4dB                                                                                    |

| 3200Hz                                                                                     | 2.7V (p-p)                                                                                                                 | - 4.3dB                                                                                    |

| 3300Hz                                                                                     | 2.5V (p-p)                                                                                                                 | - 5.3dB                                                                                    |

#### 8-G-26. Notch Filter Troubleshooting.

- 8-G-27. To check the 1010Hz notch filter, use the following procedure.

- 1. Perform steps 1-3 in paragraph 8-G-14 except input 1001500Hz at ØdBm.

- 2. Select NOISE/TONE mode on the 3586.

- 3. A70TP8 should now have a 1500Hz full-scale signal at 2.2Vp-p on a scope.

- 4. A70TP1 should have the same 1500Hz at about 4.4Vp-p.

- 5. A70TP2 should have the same 1500Hz at about 10.8Vp-p. Leave the oscilloscope on TP2.

- 6. Step (or sweep) the input source from 1001500Hz down to 1000500Hz in 10Hz increments while observing the signal at TP2.

- 7. The signal should decrease in amplitude as the frequency approaches the center of the notch until, at notch center (1010Hz), there is only noise present (usually <20mVp-p). As the input signal leaves 1001010Hz and approaches 1000500Hz, the signal should again increase in amplitude until it is about 10Vp-p at 1000500Hz.

- 8-G-28. Table 8-G-2 gives some typical amplitude values (for comparision only) of frequencies close to the notch. Sample checks from Table 8-G-2 should help to identify problem areas in the notch filter.

Table 8-G-2. Notch Filter-Frequency Versus Amplitude.

|                          | ·                          |                                    |

|--------------------------|----------------------------|------------------------------------|

| Input Frequency          | Signal Amplitude           | Signal Reduction In                |

| (A70TP8)                 | (A70TP2)                   | dB Relative to 2KHz                |

| 1200Hz                   | 9.2V (p-p)                 | – 1dB                              |

| 1150Hz                   | 5.3V (p-p)                 | – 6dB                              |

| 1100Hz                   | 1.4V (p-p)                 | 17dB                               |

| 1090Hz                   | 1.0V (p-p)                 | 20dB                               |

| 1080Hz                   | 0.65V (p-p)                | - 24dB                             |

| 1070Hz                   | 0.42V (p-p)                | 28dB                               |

| 1060Hz                   | 0.24V (p-p)                | - 32dB                             |

| 1050Hz                   | 0.12V (p-p)                | - 39dB                             |

| 1040Hz                   | 50mV (p-p)                 | – 46dB                             |

| 1030Hz                   | 20mV (p-p)                 | – 59dB                             |

| 1020Hz<br>1010Hz (NOTCH) | 10mV (p-p)<br>10mV (NOISE) | – 33dB<br>– 78dB<br>– 81dB (NOTCH) |

| 1000Hz<br>990Hz          | 10mV (p-p)                 | – 78dB                             |

| 980Hz                    | 20mV (p-p)<br>50mV (p-p)   | - 61dB<br>- 48dB                   |

| 970Hz                    | 0.12V (p-p)                | - 40dB                             |

| 960Hz                    | 0.27V (p-p)                | - 34dB                             |

| 950Hz                    | 0.43V (p-p)                | - 27dB                             |

| 940Hz                    | 0.72V (p-p)                | - 23dB                             |

| 930Hz                    | 1.1V (p-p)                 | - 19dB                             |

| 920Hz                    | 1.7V (p-p)                 | - 16dB                             |

| 910Hz                    | 2.5V (p-p)                 | - 12dB                             |

| 900Hz                    | 3.5V (p-p)                 | - 9dB                              |

| 850Hz                    | 9.0V (p-p)                 | – 1dB                              |

| 800Hz                    | 10.1V (p-p)                | ØdB                                |

Service Group G Model 3586A/B/C

#### 8-G-29. Audio Detector/Logger Troubleshooting.

8-G-30. If the Detector/Logger (A70U22) is suspected to be bad, first swap the IC (U22) with the same IC on the A4 board (A4U4). Both of these chips are in sockets for this very purpose as is also the same IC on the A21 board (A21U5). All three chips have the same part number and are completely interchangeable although some gain/offset readjustments may be required after permanent replacement.

- 8-G-31. If no changes in problem symptoms occur after swapping A70U22 with A4U4, replace the chips in their original positions to eliminate circuit readjustments. However, if WIDEBAND amplitude errors occur with these two chips swapped, or front end overload/underload problems or auto-ranging problems now exist, the A70U22 chip was bad and should be replaced.

- 8-G-32. One way to check the logger circuits for other problems is to input a full scale signal to the A70 board and trace it through the Logger Range Expander and Detector/Logger circuits. Use the following procedure.

- 1. Perform steps 1-4 in paragraph 8-G-14.

- 2. A70TP1 should have a 1850Hz signal at about 4.4Vp-p and A70TP2 should have the same signal at about 10.8Vp-p. A70TP6 should have about +0.052 VDC and U10(1) should have about -0.3 VDC. All of these values represent a full-scale signal into A70 at TP8 and may be used to locate the general area of a discrepancy.

- 8-G-33. If the problem is one of logger accuracy versus input signal amplitude, use Table 8-G-3 to verify circuit operation for input signal levels that are below the Full Scale setting. The table is for comparison purposes only.

| Input Relative<br>To Full Scale | TP8        | TP1        | TP2         | TP7         | TP6         | U10(1)     |

|---------------------------------|------------|------------|-------------|-------------|-------------|------------|

| ØdB                             | 2.2V (p-p) | 4.4V (p-p) | 10.8V (p-p) | 7.8V (p-p)  | +0.052 VDC  | -0.30 VDC  |

| - 5                             | 1.2V       | 2.5V       | 6.0V        | 5.8V        | + 0.060     | -0.35      |

| <b>- 10</b>                     | 0.68V      | 1.4V       | 3.4V        | 4.4V        | + 0.068     | - 0.40     |

| <b>- 15</b>                     | 0.38V      | 0.8V       | 1.9V        | 3.4V        | + 0.076     | - 0.45     |

| <b>- 20</b>                     | 0.22V      | 0.45V      | 1.1V        | 2.5V        | +0.084      | -0.50      |

| - 25                            | 0.12V      | 0.25V      | 0.6V        | 1.9V        | +0.092      | -0.55      |

| - 30                            | 70M∨       | 0.14V      | 0.34V       | 1.4V        | + 0.100     | -0.60      |

| ~ 35                            | 40mV       | 80mV       | 0.19V       | 1.0V        | +0.108      | -0.65      |

| <b>- 40</b>                     | 25mV       | 45mV       | 0.11V       | 0.8V        | +0.116      | -0.70      |

| <b>- 45</b>                     | 15mV       | 26mV       | 60mV        | 0.6V        | +0.124      | -0.75      |

| <b>- 50</b>                     | 10mv       | 16mV       | 40mV        | 0.45V       | +0.132      | -0.80      |

| <b>- 55</b>                     | 7mV        | 11mV       | 20mV        | 0.35V       | +0.140      | -0.85      |

| <b>- 60</b>                     | 5mV        | 6mV        | 15mV        | 0.25V       | + 0.148     | -0.90      |

| <b>- 65</b>                     | 5mV        | 5mV        | 10mV        | 0.20V       | + 0.156     | -0.95      |

| <b>- 70</b>                     | 5mV        | 5mV        | 8mV         | 0.15V       | + 0.164     | - 1.00     |

| <b>- 75</b>                     | 5mV        | 5mV        | 5mV         | 0.13V       | +0.172      | - 1.05     |

| - 80dB                          | 5mV (p-p)  | 5mV (p-p)  | 5mV (p-p)   | 0.10V (p-p) | + 0.180 VDC | - 1.10 VDC |

Table 8-G-3. A70 Signal Voltages Versus Input Signal Level.

#### Notes:

- 1. Signal frequency used for above measurements was 1850Hz at A70TP8 as set up by paragraph 8-G-14.

- 2. Voltages are for comparison purposes only.

- 3. Typical voltage gain of U10A as set by R72 is approximately -6.

- 4. Note that U10(1) changes .05 VDC for each 5dB change in input signal.

#### 8-G-34. Impulse Noise Circuit Troubleshooting.

- 8-G-35. To check the Impulse circuits up to the Comparator (U19) inputs, use the following procedure.

- 1. Perform steps 1-4 of paragraph 8-G-14.

- 2. TP2 should have a 1850Hz signal at about 10.8Vp-p.

- 3. TP4 should have the same signal rectified or about 5.4V (peak) and double the number of positive peaks (3700Hz).

- 4. TP5 should have +5.9V for a 3586A or B.

- 5. Select IMPULSE mode and press START.

- 6. TP5 should read about +3.65 vdc (THRESHOLD should still be  $\emptyset$ dBm and Full Scale should be  $\emptyset$ dBm from step 1 above).

- 7. Select other values of THRESHOLD settings from Table 8-G-4 and check TP5 for the approximate voltage indicated. Note that the voltage difference from instrument to instrument for any one frequency and full scale setting may cover  $\pm 3dB$  of CAL error. The CAL constant is always added to the value supplied to the D/A Converter as a reference for the Comparator (U19) and it cannot be zeroed out. However, the relative readings for sequential threshold steps within one instrument should remain about the same for a given frequency and full scale setting. Table 8-G-4 gives typical values for comparison purposes only. If the values for TP6 change with threshold changes and correspond approximately with Table 8-G-4, it shows that U14-U18 and U41 are probably all working.

- 8-G-36. To check the Comparator (U19) use the following procedure.